Differential Amplifier 차동 증폭기 | (2023-09-22) |

Differential Pair, 차동 쌍 | |

▷

Top

▷

전기전자공학

▷

전자회로

▷

증폭기

▷

집적회로 증폭기

▷ Top ▷ 전기전자공학 ▷ 전자회로 ▷ 증폭기 ▷ 연산증폭기 ▷ 차동 증폭기

▷ Top ▷ 전기전자공학 ▷ 전자회로 ▷ 증폭기 ▷ 연산증폭기 ▷ 차동 증폭기

1. 차동 증폭기 ㅇ 두 입력 신호의 차에 비례하여 증폭하는 회로 - 두 입력 전압의 차이의 함수로써 출력하는 증폭기 2. 차동 증폭기의 용도 ㅇ 거의 모든 연산증폭기의 입력단에 사용ㅇ 또는, - 공통모드신호 잡음 제거를 위한 회로 - 이미터 결합 논리회로(ECL)라는 고속 논리회로 - 비교기 IC의 입력단 등 3. 차동증폭기의 2가지 입력 모드 ㅇ 차동 입력 모드 (differential mode, 차동 모드) - 두 입력 차이에 따라, 출력(크기 및 극성)이 결정됨 ㅇ 동상 입력 모드 (common mode, 공통 모드) - 두 입력 단자에 불필요한 2개의 동일 신호(주파수,진폭,위상)를 인가되면, . 이 모드에서의 출력은 중첩 및 서로 상쇄됨으로써 이상적으로 `0`이됨 . 이 동작을 공통모드 제거(Common-Mode Rejection) 이라고 함 . 따라서, 원하지 않는 신호는 제거하고, 원하는 신호는 왜곡되지 않게함 - 공통모드 형태는 일반적으로 인접 도선, 전력선 등에서 유입되는 잡음임 4. 차동증폭기의 해석 방법 ㅇ 2가지 입력 모드(공통모드,차동모드)에 의한 중첩 해석 5. 차동증폭기의 특징 ㅇ 잡음,간섭 등 영향에 강함 - 단일 증폭기(one amplifier)에 비해 잡음,간섭 등에 의한 영향이 작음 ㅇ 결합커패시터 및 바이패스커패시터가 필요 없음 - 다단 증폭기에서 각 단을 용이하게 직접 결합 가능 ㅇ 구성 블록으로는, - 차동쌍, 정전류원, 능동부하 등 ㅇ 집적회로에서 제작이 보다 용이하여 널리 쓰임 - 집적회로 제작 방식은 똑같은 특성의 두 소자를 함께 배치 제작하기가 쉬움 ㅇ 집적회로에 차동증폭기 많이 사용하는 이유 - 잡음,간섭에 덜 민감 (2개의 선 간에 효과 상쇄) - 칩 면적 증대를 초래하는 바이패스 커패시터,결합 커패시터 대신에 쓰임 ㅇ 차동증폭기 능력 척도 ☞ 공통모드제거비(CMRR) 참조 6. 차동증폭기의 구현 例 (BJT 회로의 경우) ㅇ 이미터가 결합된 2개의 공통 이미터 증폭기로 구성 가능

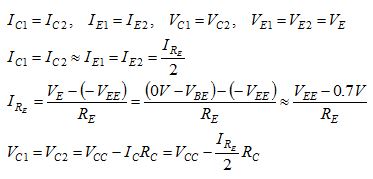

- ① 2개의 입력을 받아서, 1 또는 2개 출력을 냄 . 1개 (vout=vo1-vo2) 또는 2개 (vo1,vo2)의 출력을 발생시킴 . 이때, 출력 vout은, 입력의 차이(vi1-vi2)에 비례 - ② 동일 특성의 Tr . npn 트랜지스터 Q1,Q2는 동일 특성을 갖음 - ③ 2극(Bipolar) 공급 전압 . 양 (+VCC)과 음 (-VEE) 2개의 전원 공급 - ④ 1단 처럼 취급됨 . 두 개의 입력과 두 개의 컬렉터 전압이 있지만, 마치 한 단(stage) 처럼 취급 ㅇ (직류 바이어스 해석)

[차동 증폭기]1. 차동 증폭기 2. 차동모드 공통모드 비교 3. 차동 모드 4. CMRR

- ▷ Top (분류 펼침) New : 1,592개 분류 6,516건 해설